Difference between revisions of "Intel Nehalem (microarchitecture)"

Onnowpurbo (talk | contribs) |

Onnowpurbo (talk | contribs) |

||

| Line 10: | Line 10: | ||

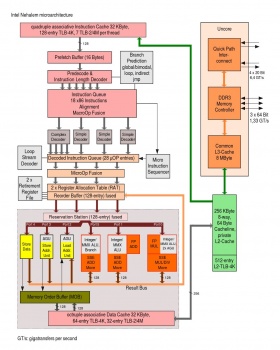

[[Image:Intel Nehalem arch.jpg|280px|right|thumb|Microarchitecture of the quad-core implementation]] | [[Image:Intel Nehalem arch.jpg|280px|right|thumb|Microarchitecture of the quad-core implementation]] | ||

Various sources have stated the specifications of processors in the Nehalem family: | Various sources have stated the specifications of processors in the Nehalem family: | ||

| + | |||

| + | * Two or four | ||

| + | ** 731 million [[transistor]]s for the quad core variant | ||

| + | * [[45 nanometer|45 nm]] manufacturing process | ||

| + | * Integrated [[memory controller]] supporting two or three memory channels of [[DDR3 SDRAM]] or four [[Fully Buffered DIMM|FB-DIMM]] channels | ||

| + | * Integrated graphics processor (IGP) located off-die, but in the same CPU package | ||

| + | * A new point-to-point processor interconnect, the [[Intel QuickPath Interconnect]], in high-end models, replacing the legacy [[front side bus]] | ||

| + | * Integration of [[PCI Express]] and [[Direct Media Interface]] into the processor in mid-range models, replacing the [[Northbridge (computing)|northbridge]] | ||

| + | * [[Simultaneous multithreading]] (SMT) by multiple cores which enables two threads per core. Intel calls this [[hyper-threading]]. Simultaneous multithreading has not been present on a consumer desktop Intel processor since 2006 with the [[Pentium 4]] and [[Pentium D#Smithfield XE|Pentium XE]]. Intel reintroduced SMT with their [[Intel_Atom#Architecture|Atom Architecture]]. | ||

| + | * Native (monolithic, i.e. all processor cores on a single die) quad- and octal-core processors | ||

| + | * The following caches: | ||

| + | ** 32 [[Kilobyte|KB]] L1 instruction and 32 KB L1 data cache per core | ||

| + | ** 256 KB L2 cache per core | ||

| + | ** 4–8 MB L3 cache shared by all cores <!-- This is about the architecture, not a specific CPU. Conroe → Penryn is a die shrink (Nehalem → Westmere)--> | ||

| + | * 33% more in-flight micro-ops than [[Intel Core 2#Conroe|Conroe]] | ||

| + | * Second-level [[branch predictor]] and second-level [[translation lookaside buffer]] | ||

| + | * Modular blocks of components such as cores that can be added and subtracted for varying market segments | ||

Revision as of 08:11, 10 February 2010

Initial Nehalem processors use the same 45 nm manufacturing methods as Penryn. A working system with two Nehalem processors was shown at Intel Developer Forum Fall 2007, and a large number of Nehalem systems were shown at Computex in June 2008.

The microarchitecture is named after the Nehalem Native American nation in Oregon. At that stage it was supposed to be the latest evolution of the NetBurst microarchitecture. Since the abandonment of NetBurst, the codename has been recycled and refers to a completely different project, although Nehalem still has some things in common with NetBurst. Nehalem-based microprocessors utilize higher clock speeds and are more energy-efficient than Penryn microprocessors. Hyper-Threading is reintroduced along with an L3 Cache missing from most Core-based microprocessors.

The first computer to use Nehalem-based Xeon processors was the Apple Mac Pro workstation announced on March 3, 2009. Nehalem-based Xeon EX processors for larger servers were expected in Q4 2009 based on initial announcements from Intel, but in November 2009 the launch of these processors was pushed back to the first half of 2010.

Mobile Nehalem-based processors were introduced in September 2009.

Technology

Various sources have stated the specifications of processors in the Nehalem family:

- Two or four

- 731 million transistors for the quad core variant

- 45 nm manufacturing process

- Integrated memory controller supporting two or three memory channels of DDR3 SDRAM or four FB-DIMM channels

- Integrated graphics processor (IGP) located off-die, but in the same CPU package

- A new point-to-point processor interconnect, the Intel QuickPath Interconnect, in high-end models, replacing the legacy front side bus

- Integration of PCI Express and Direct Media Interface into the processor in mid-range models, replacing the northbridge

- Simultaneous multithreading (SMT) by multiple cores which enables two threads per core. Intel calls this hyper-threading. Simultaneous multithreading has not been present on a consumer desktop Intel processor since 2006 with the Pentium 4 and Pentium XE. Intel reintroduced SMT with their Atom Architecture.

- Native (monolithic, i.e. all processor cores on a single die) quad- and octal-core processors

- The following caches:

- 32 KB L1 instruction and 32 KB L1 data cache per core

- 256 KB L2 cache per core

- 4–8 MB L3 cache shared by all cores

- 33% more in-flight micro-ops than Conroe

- Second-level branch predictor and second-level translation lookaside buffer

- Modular blocks of components such as cores that can be added and subtracted for varying market segments